|

CPU NOP Test |

| CPU NOP Test | Video, Info |

|

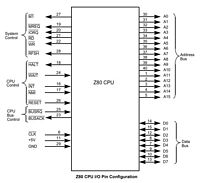

Purpose: One of the first stability tests of your Z80 breadboard build is the CPU NOP Test. NOP is short for No Operation code. The Z80 NOP machine language command is 0x00 ("0x" means hexadecimal format: 0 to 9 and A to F) in machine code. The idea is to test the Z80 CPU, the Address and Data and Control buses, the clocking circuit, and the Reset circuit. Prep: Tie the Data Bus to ground via termination resistors (4.7K work well) which will put the hex value 0x00 on pins D0-D7 of the Data Bus during every instruction Fetch cycle. The CPU Fetch cycle involves initially setting the Program Counter (PC) to zero, setting the address bus to 0x0000, and reading the first instruction and data. Normally the first instruction at 0x0000 is in ROM and prob'ly contains a jump instruction to a bootup routine, test routine, etc. In this instance it will be a No Operation (NOP) instruction.

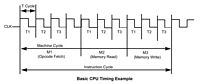

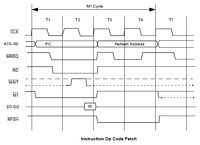

Some Info on the Instruction Fetch Process: Fetch involves setting M1, followed by a Memory Request (MREQ or MR for short). The five control LEDs in the top center of the video (in the adjacent panel) between the red address bus LEDs and the amber data bus LEDs, are labeled M1 (Fetch), MR (Memory Request), IR (I/O Request), RD (Read Request), and WR (Write Request). For a read Fetch to ROM or RAM, we expect M1, MR, and RD; a write Fetch would be M1, MR, and WR. If the Fetch is to input/output (I/O), then IR (IO Request) replaces MR. So the pattern we expect to see for a read is M1, followed by MR and RD, then just MR. The first MR and RD are for the instruction, and the second MR is for the data, if there is any; that is one reason we see MR twice. The reality is that there is a minimum number of T-cycles for each instruction; more on that later. For more info now, see page 22 of Microcomputer Design Projects by William Barden Jr.pdf

Prototype Layout: The top-left breadboard in the adjacent video is the system clock. The breadboard below it contains the LED graph bars. The next breadboard contains the 74HCT245 drivers for the bar graph LEDs so we don't load down the 3 busses. The bottom breadboard shows the Z80 Z84C00xx CPU on the right and the colour-coded wires laid out like busses to the left. There is also a small breadboard at the very bottom that connects to the Data Bus. There are 8 leads that connect to Ground via 4.7K ohm termination resistor packs. With all 8 Data Bus signals, D7 to D0 grounded, the CPU will read only 0x00 on the Data Bus. NOP uses hex code 0x00. |

Video: Z80 system executing the CPU NOP test

Clicking on the thumbnail gif above will provide an HD video (22MB, .mp4 format) showing regular clocking and single-step clocking.

Procedure: Pressing the large red double-throw button in the clock breadboard switches between regular clocking and single-stepping. Single-stepping is performed using the little red button momentary switch to the left of the large red switch. If you advance the video to about 23s when I single-step the CPU, you will see the process being performed clock cycle by clock cycle. As the CPU is single-stepped, the Program Counter (PC) increments sequentially. From the beginning, you'll see the address bus LEDs increment in value from the right to left with values of 1, 2, 4, 8, 16, etc. The data bus LEDs remain unlit because they're tied to ground (logic 0). For this Run Process to work requires that we first hold the RESET line low for at least 3 full clock cycles. (Failing to do so can result in some weird start ups.)

The CMOS-based - not NMOS-based - Z84C00xx CPU supports clock rates from DC (0 Hz) to the posted value, e.g., 6MHz.

CPU NOP Test Summary: RESET PROCESS - RESET is held low for 3 full clock cycles

RUN PROCESS - M1 is asserted low and PC is set to 0 - Address Bus is set to 0 - MR and RD are asserted low - NOP (0x00) is read from the data bus - MR is asserted again but no data is read - NOP is executed (do nothing) - PC is incremented to 1 - RUN PROCESS is repeated but now the Address Bus will set to 1

|